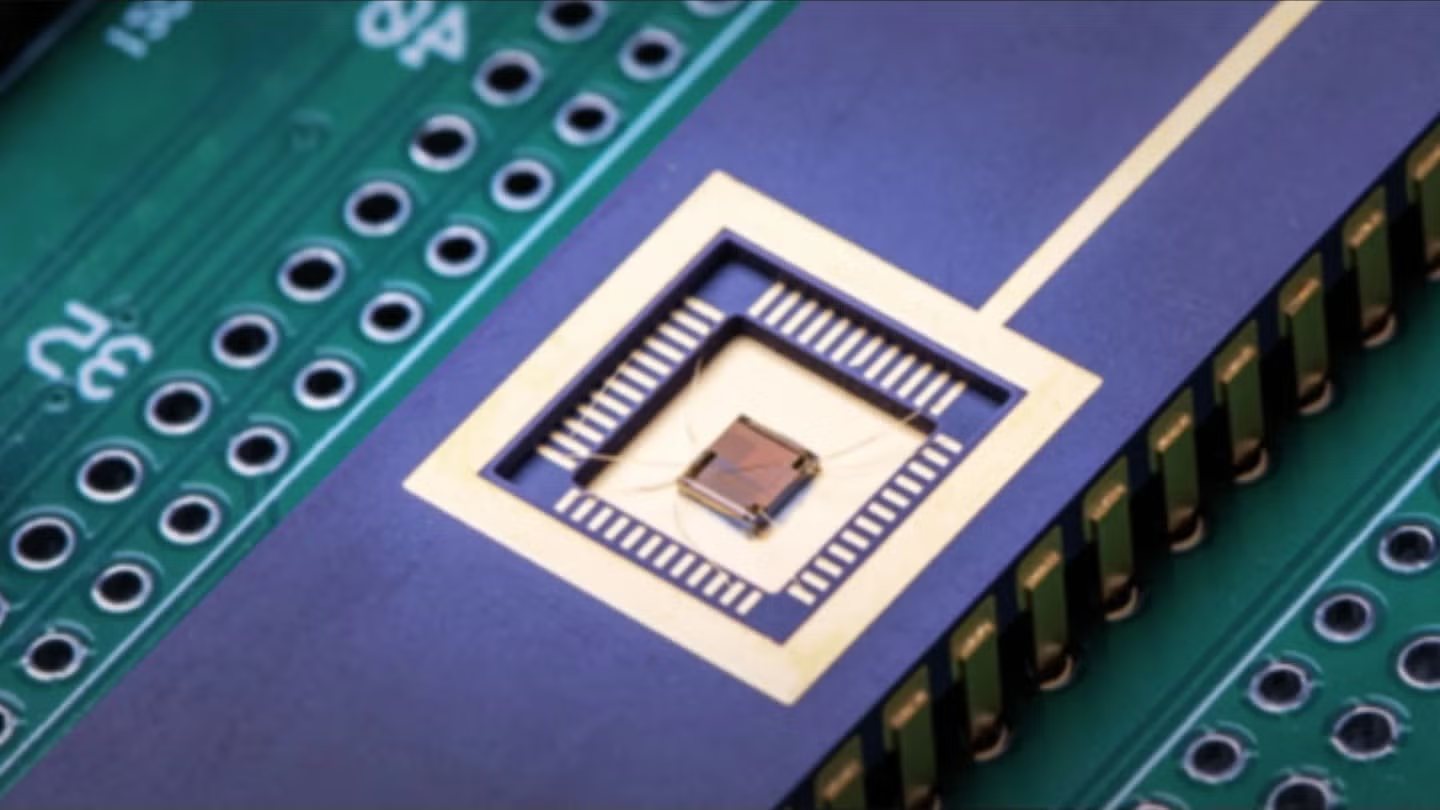

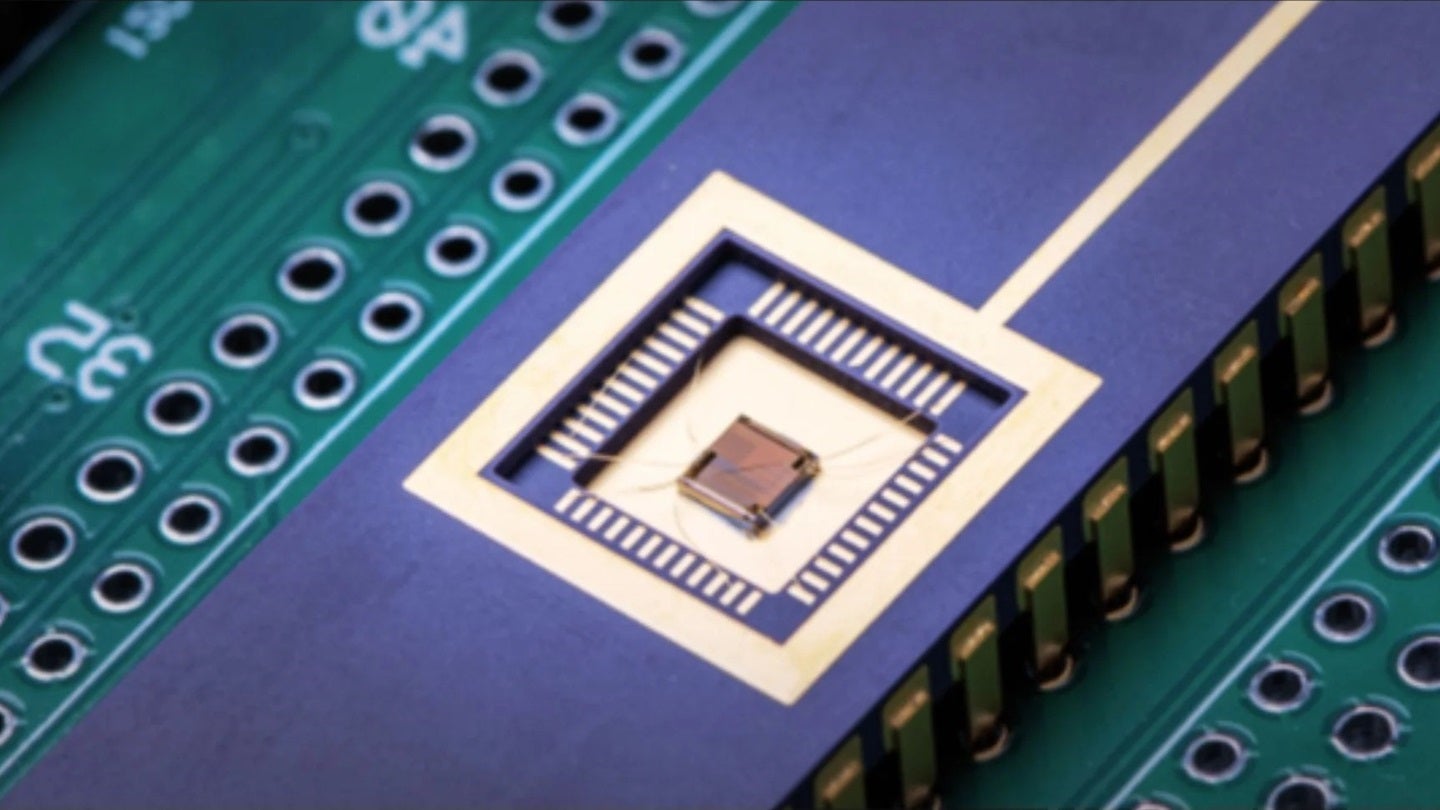

SEALSQ has launched the Quantum Protect QS7001 silicon chip on the IQT Quantum+AI 2025 Convention in New York Metropolis.

In keeping with the corporate, the QS7001 is the primary silicon chip to combine post-quantum cryptography (PQC) algorithms standardised by the US Nationwide Institute of Requirements and Know-how (NIST) straight into its {hardware}.

Entry deeper trade intelligence

Expertise unmatched readability with a single platform that mixes distinctive information, AI, and human experience.

The post-quantum chip will change into commercially accessible in mid-November 2025. Prospects can have entry to improvement kits upon the product’s launch.

The QS7001 integrates ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium) algorithms on the {hardware} degree.

SEALSQ famous that this strategy avoids reliance on software-based cryptographic execution and is meant to handle safety necessities rising from quantum computing threats.

The chip helps open {hardware} design, accommodates customized firmware, and offers an choice for hybrid cryptography migration.

Along with the Quantum Protect QS7001, SEALSQ plans to launch QVault Trusted Platform Module (TPM) variants, increasing its choices in safe {hardware} options, beginning within the first half of 2026.

NIST finalised its post-quantum requirements in August 2024, selecting Kyber, Dilithium and SPHINCS+ as the first strategies to guard towards quantum-enabled decryption of Elliptic Curve Cryptography (ECC) and Rivest Shamir Adleman (RSA).

These requirements be a part of a collection of regulatory initiatives, together with US CNSA 2.0 and White Home government orders mandating PQC adoption by 2030.

Comparable necessities from the EU and allied international locations goal a 2026–2030 migration window throughout sectors akin to finance, healthcare, infrastructure, and Web of Issues (IoT).

SEALSQ is amongst a small variety of firms with Frequent Standards EAL5+ and FIPS 140-3 safety certification for its {hardware}.

The corporate offers machine personalisation by means of safe centres in Switzerland and France, with growth deliberate in Spain, India, and the US. SEALSQ reported a deployment historical past exceeding 1.75 billion units.

Focused purposes for the QS7001 embrace defence techniques, aerospace, healthcare infrastructure, power distribution, sensible grids, and large-scale IoT authentication.

SEALSQ CEO Carlos Moreira mentioned: “By embedding post-quantum cryptography straight in {hardware}, this chip goals to set a brand new paradigm of belief and safety, securing sovereign infrastructure, healthcare, power techniques, and linked units towards the approaching quantum menace.”

In the meantime, SEALSQ is integrating its latest acquisition of the French application-specific built-in circuit (ASIC) design home IC’Alps. The corporate said that this technique will allow it to supply catalogue ICs, customized ICs, and safety mental property (IP), all inside a unified roadmap.

Quick plans embrace industrial rollout of the PQC chip, adopted by improvement of customized quantum ASICs (QASIC) and associated IP, with longer-term efforts geared toward system-level options for next-generation architectures akin to chiplet-based safety modules.

The QASIC programme will function a foundation for SEALSQ’s future post-quantum {hardware} safety modules and safe microcontrollers, with focus areas together with crucial infrastructure, defence, IoT, and AI techniques.

In September 2025, SEALSQ and Kaynes SemiCon signed a time period sheet to type SEALKAYNESQ, a three way partnership to construct India’s first safe semiconductor design and personalisation centre.